Indirect Output Voltage Control in Negative Output Elementary Super Lift Luo Converter Using PIC plus FLC in Discontinuous Conduction Mode ()

1. Introduction

The voltage lift (VL) technique is a relatively new technique to employ in dc-dc converter topologies. In the topologies discussed hitherto, the parasitic elements dissuade the output voltage and power transfer efficiency of dc-dc converters, while the VL technique can lead to improvement [1] [2] . After enduring investigation, this technique has been lucratively applied for dc-dc converters. For instance, the positive output Luo converters and negative output Luo converters are series of relatively new dc-dc step-up (boost) converters, which were developed by incorporating the VL technique. The negative output converters perform positive to negative dc-dc voltage-increasing conversion with high power density, high efficiency and cheap topology in simple structure. They are different from other existing dc-dc step-up converters and possess many advantages, including a high output voltage with small ripples. Therefore, these converters will be widely used in computer peripheral equipment, liquid crystal display (LCD), organic light-emitting diode (OLED), active-matrix LCD (AMLCD) etc. and industrial applications, especially for high output voltage projects [3] . The conventional converters may not suit for these applications as they employ a switching-boost converter with several off-chip components to generate the required negative voltages. In contrary, the converter scheme needs to achieve high performance with a minimum number of off-chip components and be capable of generating a wide range of negative voltages by varying the reference voltage.

The negative output elementary super lift Luo converter (NOESLLC) is a one of the attractive dc-dc converter and possesses the features viz. high voltage transfer gain (in geometric progression), an excellent efficiency, a suppressed inductor/capacitor ripples [4] [5] . As other dc-dc converters, the NOESLLC can also be operated in the continuous conduction mode (CCM) and discontinuous conduction mode (DCM). In CCM, the inductor current of the converter never falls to zero; a right half plane zero (RHPZ) is unavoidable. The DCM does not have RHPZ, improves system stability, avoids the reverse recovery problem of the diode and also becomes more suitable for low power application [6] [7] .

A novel negative output converter (negative-output KY buck-boost converter) has been presented [8] . Development of proportional integral derivative (PID) and fuzzy logic controllers for paralleled negative output Luo converters has been detailed and performance tested using MATLAB software [9] . The design and construction of a multivariable fuzzy controller (MFLC) for the control of a dc-dc buck converter has been presented [10] . The developed off-the-shelf hardware-based MFLC system can be used to model the variable switching structure of the buck converter. The MFLC design criterion is based on the error in output voltage and the change of error in the output voltage as inputs of the controller, and the changes in the duty cycle ratio as output of the controller. The stability of the dc-dc converters, particularly for the negative impedance induced instabilities, has been addressed [11] .

The introduced pulse adjustment technique is a digital control technique to control dc-dc converters loaded by constant power loads. This novel digital control treats converter as a digital system and regulates output voltage with the help of two predefined state variables. A genetic algorithm (GA) tuned proportional integral controller (PIC) has been devised for NOESLLC [12] . Due to the time-varying and switching nature of the NOESLLC, its dynamic behavior becomes highly non-linear. Conventional controllers are incapable of providing good dynamic performance for such a converter and hence double controller based system is required [13] . This paper proposes a proportional integral controller (PIC) plus fuzzy logic controller (FLC) for the −19.6 V output NOESLLC working in DCM. The FLC is designed for the outer (voltage) loop while the inner (current) loop is controlled by the PIC. The transient performance of the proposed controller is validated for different perturbations (line, load and component variations) and compared with PIC plus PIC. The methodologies adapted are MATLAB- Simulink simulation.

2. Analysis of DCM Operation of NOESLLC

2.1. Operation of NOESLLC

The power circuit of NOESLLC is shown in Figure 1(a), and the state/mode 1 (switch Q ON) and 2 (Q OFF) operations are respectively presented in Figure 1(b) and Figure 1(c). The state 3 (DCM) is indicated in Figure 1(d) while the inductor current is pictured in Figure 1(e). The capacitor voltage can be assumed as constant as the common selection of capacitor is much higher than the minimum demanded value.

In the Figure 1(e), T is the switching time period and d is the duty cycle. During the period , the current through the inductor is zero; switch is in OFF state, and diodes D1 and D2 are in OFF state as shown in Figure 1(d) [1] - [3] . From the Figure 1(e), the condition of DCM is expressed as

, the current through the inductor is zero; switch is in OFF state, and diodes D1 and D2 are in OFF state as shown in Figure 1(d) [1] - [3] . From the Figure 1(e), the condition of DCM is expressed as

![]() (a) (b) (c)

(a) (b) (c) ![]() (d) (e)

(d) (e)

Figure 1.The NOESLLC (a) circuit topology, (b) state 1 operation, and (c) state 2 operation, (d) equivalent circuit during turn-off mode (DCM operation) and (e) discontinuous inductor current waveform.

(1)

(1)

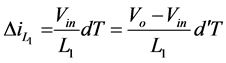

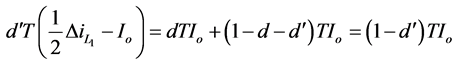

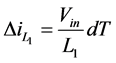

During 0 ≤ t ≤ dT, iL1 increases with slope  and during

and during , iL1 decreases with slope

, iL1 decreases with slope . Hence,

. Hence,

(2)

(2)

The above Equation (2) can be simplified as

(3)

(3)

In the steady state condition, the average capacitor current is zero. Considering the current in Co in Figure 1(b), Figure 1(c) and Figure 1(d), the following relations are obtained;

(4)

(4)

Using  from (2), and substituting

from (2), and substituting  and

and  in (4) results in (5)

in (4) results in (5)

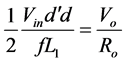

(5)

(5)

Combining (3) and (5) becomes

(6)

(6)

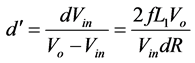

Next, defining the voltage transfer gain  in Equation (6) gives

in Equation (6) gives

(7)

(7)

Therefore,

(8)

(8)

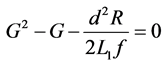

Solving the Equation (8), expresses the voltage transfer gain as follows.

![]() (9)

(9)

2.2. Condition of DCM and Validation

The condition of DCM is expressed in (1). Substitution of (7) in (1) gives,

![]() (10)

(10)

Substitution of (9) into (10) engraves as (11)

![]() (11)

(11)

The Equation (11) is the condition for DCM in the NOESLLC. This equation can be verified from the variation ratio of inductor current in CCM.

![]() (12)

(12)

where, ξ < 1 in the CCM and ξ > 1 in the DCM. Then the DCM condition is

![]() (13)

(13)

The Equation (13) agrees with Equation (11)

![]() (14)

(14)

where, ![]() for which 0 < d < 1. The maximum range of

for which 0 < d < 1. The maximum range of ![]() is derived as

is derived as

![]() (15)

(15)

Equation (15) can be depicted graphically as shown in Figure 2, where, d1 < d < d2

corresponds to the DCM. But, if![]() , then the NOESLLC operates in the CCM.

, then the NOESLLC operates in the CCM.

The derivation of variation ratio of the capacitor voltages can be expressed as (16).

![]()

Figure 2. Graphical analysis of Equation (15).

![]() (16)

(16)

![]()

where,

![]() (17)

(17)

2.3. Design of NOESLLC Circuit Elements in DCM

Using the above model equations, the detailed design and specifications of NOESLLC circuit is obtained and recorded in Table 1.

3. Design of Control Methodology

This section studies the DCM operation of NOESLLC with two different combinations of double controllers. The considered PIC plus PIC and PIC plus FLC controller combinations with the proposed scheme of control is illustrated in Figure 3. The double controller combination assumes an inner current loop with PIC to guide the inductor current and an outer voltage control loop utilizes either FLC or PIC. The voltage controller sets the mean value reference inductor current value for the inner current loop. The inputs to the outer loop controller are reference voltage and actual measured voltage. The measured current is compared with the reference current and the resulting current error is fed to the inner loop controller. The scaled control command is fed to the defined hysteresis band to generate the switching pulse for Q.

![]()

Table 1. Specifications of the NOESLLC (application in digital camera).

![]()

Figure 3. Proposed PIC plus FLC/PIC for NOESLLC in DCM.

4. Simulation Study and Results

This section deals about the simulation study and results of NOESLLC in DCM using PIC plus FLC/PIC. The NOESLLC in DCM performance is verified at various conditions viz. start-up transient, line variation, load variation, and also circuit components variations. The MATLAB/SIMULINK simulation models are performed on the NOESLLC in DCM with specifications listed in Table 1.

4.1. Start-Up Region

Figure 4 shows the simulated output voltage results of NOESLLC in DCM using the PIC plus FLC and PIC plus PIC in start-up transient region with nominal input voltage. From these figure, it is evident that the output voltage of the NOESLLC in DCM has overshoots = −0.02 V, settling time of 0.0038 s, and little steady state error around −0.12 V using PIC plus FLC. But the same converter with PIC plus PIC causes peak overshoots of −2.6 V and settling time of 6.25 ms during start-up transient region.

4.2. Line Variation

Figure 5 shows the simulated output voltage and inductor current results of NOESLLC in DCM using the PIC plus FLC and PIC plus PIC for input voltage change from 10V to 13 V at time of 0.05 s with R = 416.6 Ω. From the Figures 5(a)-(c), it is clearly focused that the output voltage of the NOESLLC in DCM has overshoots = −0.018 V, settling time of 0.0035 s, and steady state error around −0.12 V using PIC plus FLC, whereas the NOESLLC in DCM with PIC plus PIC has produced peak overshoots of −1.95 V and settling time of 6.25 ms during line disturbance region. Figure 5(c) indicates that the inductor current of NOESLLC in DCM with controllers has produced null overshoots and settling time in line variation.

![]()

Figure 4. Simulated start up output voltage responses with rated input voltage.

![]() (a)

(a)![]() (b)

(b)![]() (c)

(c)

Figure 5. Response with PIC plus FLC and PIC plus PIC for input step change from 10 V to 13 V at time of 0.05 s with R = 416.6 Ω, (a) output voltage (b) zoomed view of output voltage, and (c) inductor current.

Figure 6 shows the simulated output voltage and inductor current results of NOESLLC in DCM using the PIC plus FLC and PIC plus PIC for input voltage change from 10 V to 7 V at time of 0.05 s with R = 416.6 Ω.

From the Figures 6(a)-(c), it is clearly focused that the output voltage of the NOESLLC in DCM has overshoots = −0.021 V, settling time of 0.0032 s, and steady state error around −0.12 V using PIC plus FLC, while the NOESLLC in DCM with PIC plus PIC has produced peak overshoots of −2.12 V and settling time of 6.22 ms during line disturbance region. Figure 6(c) indicates that the inductor current of NOESLLC in DCM with controllers has produced null overshoots and settling time in line variation.

4.3. Load Variation

Figure 7 shows the simulated output voltage, output current, and inductor current results of NOESLLC in DCM using the PIC plus FLC and PIC plus PIC for load resistance change 416.6 Ω to 316.6 Ω at time of 0.05 s with input voltage of 10 V.

From the Figure 7(a), and Figure 7(b), it is clearly focused that the output voltage of the NOESLLC in DCM has overshoots = −0.02 V, settling time of 0.0034 s, and steady state error around −0.1 V using PIC plus FLC, while the NOESLLC in DCM with PIC plus PIC has produced peak overshoots of −5.12 V and settling time of 0.53 ms during load disturbance region. Figure 7(c) indicates that the inductor current and output current of NOESLLC in DCM with controllers has produced null overshoots and settling time in load variation.

Figure 8 shows the simulated output voltage, output current, and inductor current results of NOESLLC in DCM using the PIC plus FLC and PIC plus PIC for load

![]() (a)

(a)![]() (b)

(b)![]() (c)

(c)

Figure 6. Response with PIC plus FLC and PIC plus PIC for input step change from 10 V to 07 V at time of 0.05 s with R = 416.6 Ω, (a) output voltage (b) zoomed view of output voltage, and (c) inductor current.

![]() (a)

(a)![]() (b)

(b)![]() (c)

(c)

Figure 7. Response with PIC plus FLC and PIC plus PIC for load resistance change from 416.6 ohm to 316.6 ohm at time of 0.05 s with input voltage of 10 v: (a) Output voltage; (b) Zoomed view of output voltage; and (c) Inductor current.

![]() (a)

(a)![]() (b)

(b)![]() (c)

(c)

Figure 8. Response with PIC plus FLC and PIC plus PIC for load resistance change from 416.6 ohm to 516.6 ohm at time of 0.05 s with input voltage of 10 V, (a) output voltage, (b) zoomed view of the output voltage, and (c) inductor current.

resistance change 416.6 ohm to 516.6 ohm at time of 0.05 s with input voltage of 10 V. From the Figures 8(a)-(c), it is clearly focused that the output voltage of the NOESLLC in DCM overshoots = −0.018 V, settling time of 0.0038 s, and steady state error around −0.12 V using PIC plus FLC, while the NOESLLC in DCM with PIC plus PIC has produced peak overshoots of −0.385 V and settling time of 0.12 ms during load disturbance region. Figure 8(c) indicates that the inductor current and output current of NOESLLC in DCM with controllers has produced null overshoots and settling time in load variation.

Figure 9 provides the simulated instantaneous output voltage, gate pulse and the inductor current of the NOESLLC in DCM during steady state region using a PIC plus FLC. It is evident from the figure that the output voltage ripple is very small about −0.018 V and the peak to peak inductor ripple current is 0.6 A/0.61 A for the average switching frequency of 100 kHz closer to theoretical designed value listed in Table 1 and also it indicates that to keep the inductor current for the NOESLLC discontinuous.

4.4. Circuit Components Variations

Figure 10(a) and Figure 10(b) show the simulated results of output voltage of NOESLLC in DCM using both controllers in circuit components variation (i.e. inductor vary from 45 µH to 90 µH and output capacitor vary from 22 µF to 32 µF). From these results, it is understood that PIC plus PIC exhibits more overshoots while the PIC plus FLC has no over shoot.

![]()

Figure 9. Simulated response of output voltage and inductor current iL1 in steady state condition using PIC plus FLC.

![]() (a)

(a)![]() (b)

(b)

Figure 10. Circuit components variations and performance of NOESLLC in DCM: (a) Simulation output voltage when inductor variation from 45 µH to 90 µH using both controller schemes; (b) Simulation responses of output voltage when capacitor variation from 22 µF to 32 µF using both controller schemes.

Figure 11 shows the simulation results of average input current, inductor current, input voltage, output current, output voltage and efficiency of NOESLLC in DCM using PIC plus FLC. From these results, it is found that the numerical values of average input current of 0.15 A, inductor current of 0.5 A, input voltage of 10 V, output voltage of −19.6 V, average output current of −0.045 A and efficiency of 81.5% of NOESLLC in DCM using PIC plus FLC.

The time domain performance analysis of NOESLLC in DCM using both controllers is listed in Table 2. From this table, it is evident that NOESLLC in DCM using PIC plus FLC has good performance over the PIC plus PIC. Finally, the NOESLLC in DCM using PIC plus FLC has performed well in all working conditions. The membership functions for output voltage error are indicated in Figure 12. The surface view of the designed FLC is shown in Figure 13.

5. Conclusion

In this article, the analysis, design, inductor current and output voltage regulation of

![]()

Figure 11. Performance of NOESLLC in DCM-average input current, inductor current, input voltage, output current, output voltage and efficiency.

![]()

Table 2. Performance comparison of PIC plus FLC and PIC plus PIC.

![]()

Figure 12. Membership function of error voltage.

the NOESLLC operated in DCM using a variable frequency based PIC plus FLC/PIC have been successfully exhibited. The non-minimum phase behavior of the dc-dc converters results in the instable control system. In such cases the indirect regulation of the output voltage is helpful. The two-loop controller is triumph in controlling the system with improved dynamic performance. The developed PIC plus FLC regulates the output voltage of the −19.6 V NOESLLC for all possible perturbations (line, load and component variations). The merits of the designed controller are compared with PIC plus PIC using MATLAB/Simulink simulation study. There evidenced a drastic decease in peak overshoot and settling time of the start-up when PIC plus FLC is used. Similar improvement is also noticed in line and load variations.